# SystemC Synthesizable Subset Version 1.4.7

March 2016

Copyright© 2016-2018 Accellera Systems Initiative Inc. All rights reserved. Accellera Systems Initiative, 8698 Elk Grove Blvd, Suite 1 #114, Elk Grove, CA 95624, USA.

#### Notices

Accellera Systems Initiative (Accellera) Standards documents are developed within Accellera by the Technical Committee and its Working Groups. Accellera develops its standards through a consensus development process, approved by its members and board of directors, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of Accellera and serve without compensation. While Accellera administers the process and establishes rules to promote fairness in the consensus development process, Accellera does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Use of an Accellera Standard is wholly voluntary. Accellera disclaims liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other Accellera Standard document.

Accellera does not warrant or represent the accuracy or content of the material contained herein, and expressly disclaims any express or implied warranty, including any implied warranty of merchantability or suitability for a specific purpose, or that the use of the material contained herein is free from patent infringement. Accellera Standards documents are supplied "AS IS."

The existence of an Accellera Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of an Accellera Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change due to developments in the state of the art and comments received from users of the standard. Every Accellera Standard is subjected to review periodically for revision and update. Users are cautioned to check to determine that they have the latest edition of any Accellera Standard.

In publishing and making this document available, Accellera is not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Nor is Accellera undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other Accellera Standards document, should rely upon the advice of a competent professional in determining the exercise of reasonable care in any given circumstances.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of Accellera, Accellera will initiate reasonable action to prepare appropriate responses. Since Accellera Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, Accellera and the members of the Technical Committee and its Working Groups are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments for revision of Accellera Standards are welcome from any interested party, regardless of membership affiliation with Accellera. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Comments on standards and requests for interpretations should be addressed to:

Accellera Systems Initiative 8698 Elk Grove Blvd, Suite 1 #114 Elk Grove, CA 95624 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. Accellera Systems Initiative shall not be responsible for identifying patents for which a license may be required by an Accellera Systems Initiative standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Accellera is the sole entity that may authorize the use of Accellera-owned certification marks and/or trademarks to indicate compliance with the materials set forth herein.

Authorization to photocopy portions of any individual standard for internal or personal use must be granted by Accellera Systems Initiative Inc., provided that permission is obtained from and any required fee, if any, is paid

to Accellera. To arrange for authorization please contact Lynn Garibaldi, Accellera Systems Initiative, 8698 Elk Grove Blvd, Suite 1 #114, Elk Grove, CA 95624, phone (916) 670-1056, e-mail lynn@accellera.org. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained from Accellera.

Suggestions for improvements to the SystemC Synthesizable Subset are welcome. They should be sent to the Working Group's email reflector:

swg@lists.accellera.org

The current Working Group web page is:

www.accellera.org/activities/committees/systemc-synthesis

## Introduction

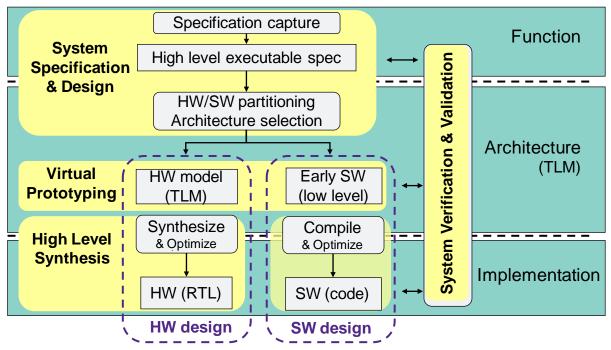

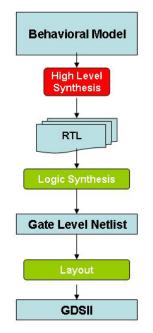

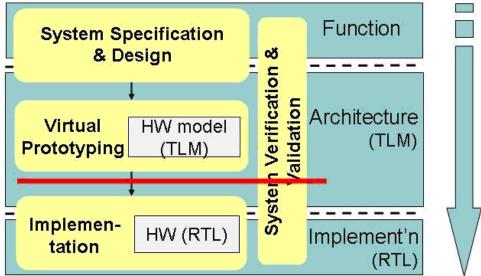

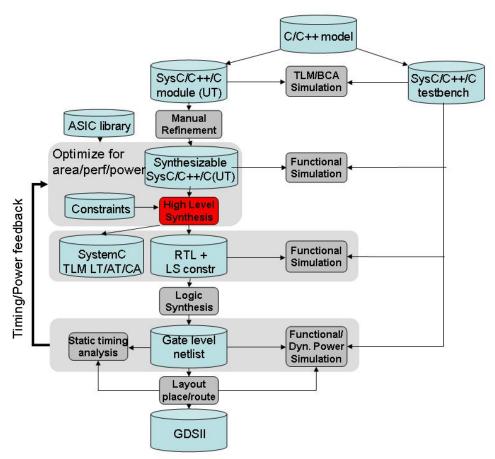

The growing popularity of SystemC for system and hardware design has spurred significant growth in the high-level synthesis (HLS) industry in the recent past. While there are multiple commercially available HLS tools that accept SystemC as an input language, the inherent difference between the description of a simulation model and that of a synthesis model presents the question of which constructs and semantics of SystemC should be supported by these tools and how.

This standard addresses this issue by defining a subset of SystemC that will be suitable for input to HLS tools. It is intended for use by hardware designers and HLS tool developers in a manner that allows hardware designers to create HLS models in SystemC that will be portable among all conforming HLS tools.

It should be noted that the intent of this version of the standard is to define a minimum subset of SystemC for synthesis, it is not meant to restrict HLS tools' support for syntax beyond this subset, including additional vendor-specific design/library components, e.g., point-to-point handshaking channels. This standard also does not define any set of tool-directives that may be required to instruct an HLS tool on how to perform synthesis on certain constructs.

This standard is defined within the existing ISO C++ and IEEE 1666 SystemC specifications. Hence, familiarity with these standards is presumed. Familiarity with various levels of abstraction and their relationship with ESL (Electronic System Level) synthesis may also be helpful in understanding this standard. A separate discussion on this topic is added as an Annex of this standard.

This standard was defined by the Synthesis Working Group of the Accellera Systems Initiative with participation from various HLS tool vendors and users. Below is the list of individuals who contributed to this standard.

#### **Participants**

The following team members drove the Draft 1.4 effort: Ashfaq Khan Jos Verhaegh Tony Kirke Mike Meredith Benjamin Carrion Schafer Bob Condon Alan P. Su Andres Takach, Chair Stuart Swan Lucien Murray-Pitts Yusuke Iguchi Masachika Hamabe Mark Johnstone Frederic Doucet

The following team members drove the Draft 1.1 ~ 1.3 effort: Mike Meredith Benjamin Carrion Schafer Alan P. Su Andres Takach, Chair Jos Verhaegh

The following team members drove the Draft 1.0 effort: Eike Grimpe Rocco Jonack Masamichi Kawarabayashi, past Chair Mike Meredith Fumiaki Nagao Andres Takach Yutaka Tamiya Minoru Tomobe

## Contents

| INTRO                                     | INTRODUCTION IV                                                                                                                                                 |                  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|

| 1 OV                                      | ERVIEW                                                                                                                                                          | 1                |  |  |

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5 \\ 1.6$  | PURPOSE<br>SCOPE<br>TERMINOLOGY<br>CONVENTIONS<br>ISOC++ IMPLEMENTATION COMPLIANCE (ISOC++ 1.4)<br>SYSTEMC LRM COMPLIANCE                                       | 1<br>1<br>3<br>3 |  |  |

| 2 TR                                      | ANSLATION UNITS                                                                                                                                                 | 5                |  |  |

| $\begin{array}{c} 2.1 \\ 2.2 \end{array}$ | TRANSLATION UNITS AND THEIR ANALYSIS<br>PRE-PROCESSING DIRECTIVES                                                                                               |                  |  |  |

| 3 MC                                      | DULES                                                                                                                                                           | 6                |  |  |

| $3.1 \\ 3.2 \\ 3.3$                       | MODULE DEFINITIONS<br>DERIVING MODULES<br>MODULE HIERARCHY                                                                                                      | 9                |  |  |

| 4 PR                                      | OCESSES 1                                                                                                                                                       | 10               |  |  |

| $\begin{array}{c} 4.1 \\ 4.2 \end{array}$ | SC_METHOD                                                                                                                                                       |                  |  |  |

| 5 PR                                      | EDEFINED CHANNELS, INTERFACE PROPER AND PORTS 1                                                                                                                 | 15               |  |  |

| $5.1 \\ 5.2 \\ 5.3$                       | PREDEFINED CHANNELS                                                                                                                                             | 15               |  |  |

| 6 TY.                                     | PES 1                                                                                                                                                           | 17               |  |  |

| $6.1 \\ 6.2 \\ 6.3$                       | FUNDAMENTAL TYPES       1         COMPOUND TYPES       2         SYSTEMC DATATYPES       2                                                                      | 20               |  |  |

| 7 DE                                      | CLARATIONS                                                                                                                                                      | 30               |  |  |

| 7.1                                       | Specifiers                                                                                                                                                      | 30               |  |  |

| 8 DE                                      | CLARATORS E                                                                                                                                                     | 32               |  |  |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5           | Type names       a         Ambiguity resolution.       a         Kinds of declarators       a         Function definition       a         Initializers.       a | 32<br>32<br>32   |  |  |

| 9 EX                                      | PRESSIONS                                                                                                                                                       | 34               |  |  |

| $9.1 \\ 9.2 \\ 9.3 \\ 9.4$                | FUNCTION CALL       3         EXPLICIT TYPE CONVERSION       3         TYPEID       3         UNARY EXPRESSIONS AND OPERATORS       3                           | 34<br>35         |  |  |

| 9.5          | POINTER-TO-MEMBER OPERATORS                                | 36 |

|--------------|------------------------------------------------------------|----|

| 9.6          | MULTIPLICATIVE, ADDITIVE, SHIFT, RELATIONAL, EQUALITY, AND |    |

| Assig        | NMENT OPERATORS                                            | 36 |

| 9.7          | BITWISE AND LOGICAL AND/OR/XOR OPERATORS                   | 36 |

| 9.8          | CONDITIONAL OPERATOR                                       | 36 |

| 9.9          | COMMA OPERATOR                                             | 36 |

| 10 S         | TATEMENTS                                                  | 37 |

| 10.1         | LABELED STATEMENT                                          | 37 |

| 10.2         | COMPOUND STATEMENT                                         | 37 |

| 10.3         | SELECTION STATEMENTS                                       | 37 |

| 10.4         | ITERATION STATEMENTS                                       | 37 |

| 10.5         | JUMP STATEMENTS                                            | 37 |

| 10.6         | DECLARATION STATEMENT                                      | 37 |

| 10.7         | EXCEPTION HANDLING STATEMENTS                              | 38 |

| 11 N         | IAMESPACES                                                 | 39 |

| 11.1         | NAMESPACE DEFINITION                                       | 39 |

| 11.2         | NAMESPACE ALIAS                                            | 39 |

| 11.3         | THE USING DECLARATION                                      | 39 |

| 11.4         | USING DIRECTIVE                                            | 39 |

| 12 C         | LASSES                                                     | 40 |

| 12.1         | CLASS NAMES                                                | 40 |

| 12.2         | CLASS MEMBERS                                              |    |

| 12.3         | MEMBER FUNCTIONS                                           |    |

| 12.4         | STATIC MEMBERS                                             |    |

| 12.5         | UNIONS                                                     |    |

| 12.6         | BIT-FIELDS                                                 |    |

| 12.7         | NESTED CLASS DECLARATIONS                                  | 40 |

| 12.8         | LOCAL CLASS DECLARATIONS                                   | 40 |

| 12.9         | NESTED TYPE NAMES                                          | 40 |

| 12.10        | DERIVED CLASSES                                            | 41 |

| 12.11        | Member access control                                      | 41 |

| 12.12        | SPECIAL MEMBER FUNCTIONS                                   | 41 |

| 13 C         | VERLOADING                                                 | 43 |

| 13.1         | OVERLOADABLE DECLARATIONS                                  | 43 |

| 13.2         | DECLARATION MATCHING                                       | 43 |

| 13.3         | OVERLOAD RESOLUTION                                        | 43 |

| 13.4         | Address of overloaded function                             |    |

| 13.5         | OVERLOADED OPERATORS                                       |    |

| 13.6         | BUILT-IN OPERATORS                                         | 44 |

| 14 T         | 'EMPLATES                                                  | 45 |

| 14.1         | TEMPLATE PARAMETERS                                        | 45 |

| 14.1<br>14.2 | NAMES OF TEMPLATE SPECIALIZATIONS                          |    |

| 14.3         | TEMPLATE ARGUMENTS                                         |    |

| 14.4         | TYPE EQUIVALENCE                                           |    |

|              | -                                                          | -  |

| $14.5 \\ 14.6 \\ 14.7 \\ 14.8$              | TEMPLATE DECLARATIONS4NAME RESOLUTION4TEMPLATE INSTANTIATION AND SPECIALIZATION4FUNCTION TEMPLATE SPECIALIZATIONS4 | 6<br>7<br>7 |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------|

| 15 L                                        | IBRARIES 4                                                                                                         | 8           |

| $\begin{array}{c} 15.1 \\ 15.2 \end{array}$ | STANDARD C AND C++ LIBRARIES                                                                                       |             |

|                                             | A LEVELS OF ABSTRACTION IN SYSTEMC DESIGN AND DUCTION TO HIGH-LEVEL SYNTHESIS (INFORMATIVE)                        | 0           |

| A.1                                         | INTRODUCTION TO ABSTRACTION LEVELS                                                                                 | 0           |

| A.2                                         | INTRODUCTION TO HIGH-LEVEL SYNTHESIS                                                                               |             |

| A.3                                         | VISION FOR HIGH-LEVEL DESIGN                                                                                       |             |

| A.4                                         | ABSTRACTION LEVEL DETAILS                                                                                          |             |

| A.4.1                                       | FUNCTION LEVEL                                                                                                     |             |

| A.4.1.                                      |                                                                                                                    |             |

| A.4.1.                                      |                                                                                                                    |             |

| A.4.2                                       | ARCHITECTURE LEVEL                                                                                                 | -           |

| A.4.3                                       | TRANSACTION LEVEL MODELING                                                                                         |             |

| A.4.4                                       | IMPLEMENTATION LEVEL                                                                                               |             |

| A.4.4.                                      |                                                                                                                    | -           |

| A.4.4.                                      |                                                                                                                    | -           |

| A.4.4.                                      |                                                                                                                    | -           |

| ANNEX<br>DEFINI                             |                                                                                                                    | Т           |

| ANNEX                                       | C REFERENCES                                                                                                       | 0           |

## 1 Overview

### 1.1 **Purpose**

In this standard document, the Synthesis Working Group (SWG) of the Accellera Systems Initiative has defined a subset of SystemC that is appropriate for synthesis. This is intended to be useful for hardware designers to accelerate the modeling process with SystemC and for EDA tool developers to develop SystemC compliant high-level synthesis (HLS) tools. The synthesizable subset of SystemC will be defined within the existing ISO C++ and IEEE Std 1666 SystemC specifications. Hence, familiarity with these standards is presumed.

There are a wide variety of resources available to assist users in modeling with SystemC, including the IEEE Std 1666 Language Reference Manual (LRM), user guides of the HLS tools, and a number of books on SystemC modeling. This document is intended to fill a gap by defining a standard for creating synthesizable hardware description in SystemC, allowing a smooth transition between abstract modeling in SystemC and synthesizable description.

### 1.2 **Scope**

The synthesizable subset defines the syntactic elements in ISO C++, as described in ISO/IEC 14882:2003 [1] and SystemC, as described in IEEE Std 1666-2011 [2], that are appropriate for use in SystemC code intended for input to HLS tools. In some cases, there are references to ISO/IEC 14882:2011 [3] for very specific items that were widely available before they were standardized in 2011. For example, the type *long long* and the behavior that division truncates towards zero (0). The intent of this version of the standard document is to describe a minimum initial subset which can be supported by tools. It is not meant to restrict synthesis support for syntax beyond this subset.

The synthesizable subset of SystemC currently covers the register transfer level (RTL) and the behavioral level. More abstraction levels are also discussed in this document to provide context.

### 1.3 **Terminology**

### 1.3.1 Base Standards

The following standards contain provisions which, through reference in this text, are included in this standard. At the time of publication, the editions indicated were valid.

- ISO/IEC 14882:2003, Programming languages C++, hereinafter called *ISOC*++.

- ISO/IEC 14882:2011, Programming languages C++, hereinafter called *ISOC*++11.

- IEEE Std1666-2011, SystemC, hereinafter called the SystemC LRM.

### 1.3.2 Word usage

The word <u>shall</u> indicates mandatory requirements strictly to be followed to conform to the standard and from which no deviation is permitted (<u>shall</u> equals <u>is required to</u>; <u>shall not</u> equals <u>is not permitted to</u>).

The word <u>should</u> indicates a certain course of action is preferred, but is not a mandatory requirement; or (in the negative form, <u>should not</u>) that a certain course of action is permitted, but such usage is discouraged (<u>should</u> equals <u>is recommended that</u>).

The word <u>may</u> indicates a course of action permissible within the limits of the standard (<u>may</u> equals <u>is permitted</u>).

The word <u>application</u> is a C++ program written by an end user that uses the SystemC, TLM-1, and TLM-2.0 class libraries, i.e., it uses classes, functions, or macros defined in the SystemC LRM.

The word *implementation* means any specific implementation of the full SystemC, TLM-1, and TLM-2.0 class libraries, as defined in the SystemC LRM, of which only the public interface need be exposed to the application.

The word <u>design</u> is used to mean a SystemC design written by an end user that describes hardware in conformance with this standard.

A synthesis tool is said to <u>accept</u> a SystemC construct if it allows that construct to be a legal input; it is said to <u>interpret</u> the construct (or to provide an <u>interpretation</u> of the construct) if it accepts that construct and produces a corresponding synthesis result.

The word <u>synthesis tool</u> is used to mean a high-level synthesis tool that <u>accepts</u> and <u>interprets</u> a <u>design</u> in conformance with this standard.

The term <u>*call*</u> is taken to mean call directly or indirectly. Call indirectly means call an intermediate function that in turn calls the function in question, where the chain of function calls <u>*may*</u> be extended indefinitely. Similarly, <u>*called from*</u> means called from directly or indirectly.

The term <u>*class*</u> is used to cover the C++ keywords *class* or *struct*.

Except where explicitly qualified, the term <u>derived from</u> (or <u>inherited from</u>) is taken to mean derived directly or indirectly from a <u>class</u>. Derived indirectly from means derived from one or more intermediate base <u>classes</u>.

A <u>synthesis refinement</u> in this document imposes a restriction or alteration upon some other standard (e.g., the SystemC LRM or the ISOC++ standard) in order to subset the otherwise supported methods to describe behavior to a set that can be implemented in hardware.

The word <u>deprecated</u> is used to describe a feature that is superseded by a better, safer, easier to use alternative. Use of the <u>deprecated</u> feature is strongly discouraged and future standards <u>may</u> make such use illegal.

### **1.3.3** Construct Categories

The constructs in this standard *shall* be categorized as:

Supported: A synthesis tool shall interpret the construct.

*Ignored*: A <u>synthesis tool shall</u> accept the construct, but <u>may</u> choose not to interpret the construct. The mechanism, if any, by which a <u>synthesis tool</u> notifies (warns) the user of such constructs is not defined in this standard.

*Not Supported*: A <u>synthesis tool may</u> choose not to accept the construct. The behavior of the <u>synthesis tool</u> upon encountering such a construct is not defined in this standard. For example, a <u>synthesis tool may</u> choose to fail upon encountering such a construct; alternatively, it <u>may</u> choose to accept/interpret such a construct. It <u>should</u> be noted that even if a <u>synthesis tool</u> accepts/interprets some of the constructs that are *Not Supported*, a <u>design</u> that uses such constructs runs the risk of losing portability. However, it is also possible that, in a future revision of this standard, some of the constructs that are *Not Supported* now will be *Supported*.

Supported with Restrictions: A <u>synthesis tool shall</u> interpret the construct with certain restrictions. This means, instances of the construct which are within the restrictions, as set forth by this standard, are Supported; while instances that violate these restrictions are either *Ignored* or Not Supported. Unless explicitly categorized as *Ignored*, the violating instances are Not Supported. A construct that is Supported with Restrictions is also said to have Restricted Support.

### 1.4 **Conventions**

This document uses the following conventions:

- a) The body of the text of this standard uses *italics* to denote SystemC or C++ reserved words (e.g., *sensitive* and *SC\_MODULE*).

- b) The body of the text of this standard also uses <u>italics underlined</u> to highlight definitions (e.g., <u>application</u> or <u>design</u>) or to visually reinforce key terms (e.g., <u>shall</u>, <u>should not</u>, and <u>synthesis refinement</u>).

- c) The body of the text of this standard uses *bold italics* to visually reinforce construct categories (e.g., *Supported* and *Ignored*).

- d) The text of the SystemC examples and code fragments is represented in a fixed-width font.

- e) An outlining box with the title "NOTE" provides an informative expansion of certain key concepts. They are intended to assist in understanding of a construct, but are not intended as a restriction or enhancement of a <u>synthesis tool</u>

- f) The examples that appear in this document under "*Example:*" are for the sole purpose of demonstrating the syntax and semantics of SystemC for synthesis. It is not the intent of this standard to demonstrate, recommend, or emphasize coding styles that are more (or less) efficient in generating an equivalent hardware representation. In addition, it is not the intent of this standard to present examples that represent a compliance test suite or a performance benchmark, even though these examples are compliant to this standard (except as noted otherwise).

## 1.5 **ISOC++ Implementation Compliance (ISOC++ 1.4)**

The ISOC++ Section 1.4 Implementation Compliance applies to the synthesis subset.

### **1.5.1** Implementation-defined behavior (ISOC++ 1.3.5)

Simulation of the <u>design</u> is based on C++ compilers on specific computer platforms. In most cases, such platforms have converged on certain default implementation-defined behaviors

and <u>synthesis tools</u> are required to either adhere to those behaviors or provide warnings to the effect that a different implementation-defined behavior is being followed. An example of an implementation-defined behavior is the bit-width of fundamental integer types.

### **1.5.2** Undefined behavior (ISOC++ 1.3.12)

The presence of undefined behavior <u>may</u> lead to differences between simulation and synthesis and differences in results from different <u>synthesis tools</u>. Unless this standard provides a <u>synthesis refinement</u> that provides a definition, such undefined behavior is **Not Supported** In some cases, undefined behavior is assumed to be not present in the <u>design</u>. One specific example is division by zero (0). <u>Synthesis tools may</u> assume that such a condition will not be present during simulation of the <u>design</u> and treat such a condition as a don't care.

### **1.5.3** Unspecified behavior (ISOC++ 1.3.13)

The presence of unspecified behavior <u>may</u> lead to differences between simulation and synthesis results and differences in results from different <u>synthesis tools</u>. An example is the order of evaluation of arguments to a function is not specified. In ISOC++, the implementation is not required to document which behavior occurs.

### 1.6 SystemC LRM Compliance

This section describes some general terms that are used in the SystemC LRM that have some similarities with terms used in ISOC++ as described in Section 1.5.

### **1.6.1** Implementation-defined (SystemC LRM 3.2.1)

The description in Section 1.5.1 applies. In general, most of the implementation-defined items in the SystemC LRM do not affect synthesis. One item that does affect synthesis is the type for limited precision (SystemC LRM 7.2.2). In that case, this standard only supports one implementation as specified in Section 6.3.

### 1.6.2 Undefined

The description in Section 1.5.2 applies when the word <u>undefined</u> is used in the context of the behavior not being defined.

### 1.6.3 Error

The word error is sometimes used interchangeably with the word undefined in the SystemC LRM. In many cases, an *error* refers to a compilation or simulation error. *Synthesis tools* assume that such conditions will not be present and treat such condition as a don't care, unless the *synthesis tools* are able to prove that the error is present, in which case they *may* issue an error appropriately.

## 2 Translation units

### 2.1 **Translation units and their analysis**

The text of a <u>design</u> is, as described by ISOC++ Section 2, kept in units called source files. A source file together with all included sources, less any lines skipped through preprocessor macros, is known as a translation unit.

A translation unit <u>shall</u> be specified using the basic source character set, as described by ISOC++ Section 2. However, the trigraph sequences, as described by ISOC++ section 2.3, and alternative tokens are *Not Supported*. Furthermore, instance names using Universal-Character-Name as described in ISOC++ Section 2 and ISOC++ Annex E are <u>synthesis tool</u>-dependent and, therefore, *Not Supported*.

Using multiple translation units to describe a <u>design</u> is **Supported**. This standard, however, does not specify how a user will provide the translation-unit information to the <u>synthesis tool</u>.

The use of the keyword *extern* to refer to a declaration in a different scope within the same translation unit or in a different translation unit is *Supported*. However, the use of libraries (pre-compiled binary files) is *Not Supported*, and a <u>design shall</u> contain all the source files required for synthesis (with the exception of SystemC implementation and C/C++ native library files).

The use of *extern* string-literals for linkage specification (e.g., extern "C", extern "C++") is *Not Supported* (ISOC++ 7.5).

The functions *main* and *sc\_main* are *Ignored*.

### 2.2 **Pre-processing directives**

The full set of C/C++ preprocessing directives is *Supported* (refer to Clause 16 in [3]). A <u>synthesis tool shall</u> recognize pragma directives (#pragma). It <u>may</u> ignore or process pragma directives.

A <u>Synthesis tool shall</u> predefine the following macro names:

| 1. | STDC         | : The value is implementation-dependent.                   |

|----|--------------|------------------------------------------------------------|

| 2. | cplusplus    | : The value is implementation-dependent.                   |

| 3. | SC_SYNTHESIS | : The version of the synthesis subset, in a year and month |

|    |              | format such as 201601L.                                    |

| 4. | SYNTHESIS    | : The value is implementation-dependent.                   |

|    |              |                                                            |

#### NOTE

The expected use of the \_\_SYNTHESIS\_\_ and SC\_SYNTHESIS macros is to guard nonsynthesizable code. The version contained in SC\_SYNTHESIS is meant to select different versions of the same behavior that depend on updates to the synthesis subset.

## **3** Modules

This section specifies the core SystemC language subset used in a <u>design</u> for modeling a hardware element. In this document *sc\_module* and module are used interchangeably. A single hardware element is represented by a module and a system is described by creating a hierarchy of modules stemming from a parent module.

This section does not limit the optimizations that can be performed on the model, the scope of which depends on the <u>synthesis tool</u> itself. Irrespective of the level of optimizations performed, the result of the synthesis <u>should</u> have the same functionality as the input model, but <u>may</u> have different sequential timed behavior.

### 3.1 Module definitions

A SystemC module, as defined in the SystemC LRM definition, <u>may</u> contain the port-level interfaces, any required internal storage elements, and any required behavior for that module.

The *Supported* possibilities for module definition are as follows.

- Use of the *SC\_MODULE* macro;

- Derivation of a *class* from *sc\_module*.

In addition to the above, templated module definition has *Restricted Support*. The restriction is that, for the top-level module, only modules that have been instantiated (as defined in ISOC++ 14.7.1 and 14.7.2) or have been explicitly specialized (as defined in ISOC++ 14.7.3) are *Supported*. For non-top-level modules, templated module definition is *Supported*.

Template specialization and partial-specialization of modules is also Supported.

#### NOTE

In C++, template classes and functions are not instantiated until they are implicitly instantiated (as defined in ISOC++14.7.1) or are explicitly instantiated (as defined in ISOC++14.7.2).

```

In C++, template classes and functions can be explicitly specialized (as defined in ISOC++ 14.7.3) using the "template <>" declaration (i.e., the class is fully specialized).

```

Examples of implicit and explicit instantiations and explicit specialization are shown below. The most common form for synthesis is the use of implicit instantiation for submodules and implicit instantiation of the template top-level module in the testbench (from main or sc\_main). If the testbench is not present or is excluded from analysis, the use of an explicit instantiation would be indicated. Note that explicit specializations are less common and only indicated when there is an advantage in providing a specialized version of the module (the example below is not an illustration of such a case).

```

template <int N>

SC_MODULE (design) {

sc_in<int> a;

sc_out<int> c;

```

```

void add() { c = a + N; }

SC_CTOR(design) : a("a"), c("c") {

SC METHOD(add);

sensitive << a;

}

};

template class design<5>; // EXPLICIT INSTANTIATION

int main() {

// IMPLICIT INSTANTIATION

design<7> x;

}

template<> SC MODULE(design<3>) { // EXPLICIT SPECIALIZATION

sc in<int> a;

sc out<int> c;

void add() { c = a + 3; }

SC_CTOR(design) : a("a"), c("c") {

SC_METHOD(add);

sensitive << a;</pre>

}

};

```

### 3.1.1 Selecting the top of a design hierarchy

This standard does not define any method for specifying the top-level module(s) of a *design*. The mechanisms for specifying the top-level module(s) of a *design* are *synthesis tool* dependent.

### 3.1.2 Module member specification

The module member specification contains a set of member declarations and definitions. Any valid and legal SystemC macros are *Supported*.

### **3.1.3** Module declarative items

### 3.1.3.1 Module special functions

Module constructors are *Supported*. Module destructors are *Ignored*. The other two special member functions, namely the *Copy Constructor* and the *Assignment Operator*, as defined in ISO C++ Section 12, are disabled for *sc\_module* by the SystemC LRM 5.2.2, hence, they are disabled for *sc\_module*.

### 3.1.3.2 Communication between processes through module member variables

Within a module, processes <u>shall</u> only communicate with each other through member variables which are of type <u>sc\_signal</u>. Non-const variables which are not of <u>sc\_signal</u> type <u>shall</u> be read and written by only one process.

### 3.1.3.3 Communication between modules

Communication between modules *shall* only be through *sc\_in* and *sc\_out*, which are to be bound to *sc\_signals*.

Calling the binding function for a port that is a data member of a module from the constructor of the parent to the module is *Supported*.

Other cases of access to module non-const data members from outside the module is *Not Supported*.

### 3.1.3.4 sc\_port, sc\_export, sc\_signal, and other channels

- Instantiation of a sc\_port or directly deriving from sc\_port in a <u>design</u> is Not Supported.

- Instantiation of a sc\_export or directly deriving from sc\_export in a <u>design</u> is Not Supported.

The specialized ports and channels are described in Section 5 of this standard.

#### NOTE

Ports represent the externally visible interface to a module and are used to transfer data into and out of the module. Specialized ports using the *sc\_in* and *sc\_out* constructs are used to describe this pin level description at the module boundary.

Signals can be used to interface between processes and modules. Signals are declared using the *sc\_signal* construct.

### 3.1.3.5 Module constructor

Module constructor declaration through the use of the *SC\_CTOR* macro or explicit declaration of a constructor special function either with no argument or a single argument for the module name are *Supported*. Explicit declaration of a constructor special function with more than one argument or an argument that is not a module name is *Not Supported*.

Every module declaration <u>shall</u> contain one declaration or definition of a constructor member function. Multiple constructor declarations or definitions are *Not Supported*.

Within a constructor of an *SC\_MODULE* and functions called from the constructor, the following operations are *Supported* to construct module hierarchy:

- Constructor calls of *sc\_in/sc\_out/sc\_signal/SC\_MODULE*.

- Initialization of pointers to *SC\_MODULE*s with *SC\_MODULE* objects allocated using the *new* operator.

- Port bindings between *sc\_signal/sc\_in/sc\_out* using *bind()* and *operator()*.

- Creation of processes using *SC\_THREAD/SC\_CTHREAD/SC\_METHOD* and sensitivity specification as described in Section 4.

In addition, initialization of references and constant data members in the constructor initializer list is *Supported*.

In contrast to normal C++ practice, writing to data members other than initialization of *SC\_MODULE* pointers, signals, or ports of a module from inside the *SC\_MODULE* constructor are *Not Supported*. Overwriting a variable of type pointer to *sc\_module* after initialization is *Not Supported*.

#### NOTE

Initialization of an *SC\_MODULE* data member should be performed within the reset portion of an *SC\_THREAD*, *SC\_CTHREAD*, or sequential *SC\_METHOD* in order to have the initialization be performed at reset time

### 3.2 **Deriving modules**

Deriving modules, as defined in SystemC LRM 5.2.3, is Supported.

Examples:

```

// Deriving a module:

SC_MODULE( BaseModule ) {

sc_in< bool > reset;

sc_in_clk clock;

BaseModule ( const sc module name& name

)

: sc_module( name_ )

{ }

};

class DerivedModule : public BaseModule {

void newProcess();

SC HAS PROCESS( DerivedModule );

DerivedModule( sc_module_name name_ )

: BaseModule( name ) {

SC_CTHREAD( newProcess, clock.pos() );

reset_signal_is( reset, true ) ;

}

};

```

### 3.3 Module hierarchy

Module hierarchy, as defined in SystemC LRM 5.3.4, is Supported.

Port binding, as described in SystemC LRM 4.1.3 is *Supported*. Note that positional binding (as described in SystemC LRM Annex C as a deprecated feature) is *Not Supported*.

### 4 Processes

The use of the *SC\_THREAD*, *SC\_CTHREAD*, and *SC\_METHOD* constructs to create processes is *Supported with Restrictions*. The use of *sc\_spawn()* to create processes is *Not Supported*.

None of the uses of *sc\_process\_handle* are synthesizable, hence such usage is *Not Supported*. Consequently, the use of *suspend()*, *resume()*, *enable()*, *disable()*, *kill()*, *reset()*, and *throw\_it()* is also *Not Supported*.

### 4.1 SC\_METHOD

In a SystemC <u>design</u>, the body of an SC\_METHOD is executed whenever its sensitivity condition is met. The logic inferred by a <u>synthesis tool</u> for an SC\_METHOD depends on both the sensitivity condition and the form of the SC\_METHOD body.

As a <u>synthesis refinement</u>, all paths through an *SC\_METHOD* <u>shall</u> either be combinational or sequential. An *SC\_METHOD* with a mix of combinational and sequential paths is *Not Supported*.

For *SC\_METHOD*, *reset\_signal\_is* and *async\_reset\_signal\_is* are *Not Supported*. Modeling of reset behavior is done using the coding styles described below.

### 4.1.1 Combinational SC\_METHOD

An *SC\_METHOD* can used to describe combinational logic, with the *SC\_METHOD* sensitive to any change in the signals in its sensitivity list.

As a <u>synthesis refinement</u>, the sensitivity list here <u>shall</u> be static and include all signals that are read in the body of the method. This is done to avoid accidental latching, which would lead to synthesis and simulation mismatches.

// Example of combinational SC\_METHOD

SC\_METHOD(comb); sensitive << a << b << c;

void comb() { f.write(a.read()+b.read()+c.read()); }</pre>

### 4.1.2 Sequential SC\_METHOD

The body of a sequential *SC\_METHOD* <u>shall</u> consists of two mutually exclusive branches based on the clock and reset conditions.

### 4.1.2.1 Sequential SC\_METHOD with synchronous reset

A sequential *SC\_METHOD* with synchronous reset <u>shall</u> be sensitive to only a positive or negative edge of a clock signal.

// Example of sequential SC\_METHOD with synchronous reset:

SC\_METHOD(dff); sensitive << clk.pos();</pre>

```

void dff() {

if (rst == 0) {

// reset signals

} else {

// assign signals

}

}

```

### 4.1.2.2 Sequential SC\_METHOD with asynchronous reset

A sequential *SC\_METHOD* with asynchronous reset <u>shall</u> be sensitive to only a positive or negative edge of a clock signal and a positive or negative edge of a reset signal.

```

// Example of sequential SC_METHOD with asynchronous reset

SC_METHOD(dff); sensitive << clk.pos() << rst.neg();

void dff() {

if (rst == 0) {

// reset signals

} else {

// assign signals

}

}</pre>

```

### 4.2 SC\_THREAD and SC\_CTHREAD

SystemC allows the usage of the *SC\_THREAD* and *SC\_CTHREAD* macros to create unspawned processes which run from the start of simulation until the end of simulation.

*SC\_CTHREAD* and *SC\_THREAD* are *Supported with Restrictions*. They are *Supported*, as specified in the SystemC LRM, when the following restrictions regarding the process sensitivity and process body are met (in addition to the other restrictions mentioned throughout this standard, e.g., regarding break/continue/goto statements).

NOTE

In earlier versions of SystemC, *SC\_THREAD* and *SC\_CTHREAD* differed in their reset behavior. Currently, there are minor syntax differences between the two, but for synthesis purposes, they have the same expressiveness.

### 4.2.1 Clock and Reset

The sensitivity of the process <u>shall</u> be specified in the constructor of the SC\_MODULE enclosing the process. A process <u>shall</u> be statically sensitive to exactly one clock edge and <u>shall</u> have at least one reset specification. A process <u>may</u> have at most one synchronous reset specification and at most one asynchronous reset specification. Different SC\_(C)THREADs <u>may</u> be sensitive to different clocks and resets, i.e., an SC\_MODULE <u>may</u> contain multiple clocks.

The use of *reset\_signal\_is* and *async\_reset\_signal\_is* to specify reset sensitivity is **Supported**.

SC\_THREAD example:

```

SC_THREAD(thread_process);

sensitive << clk.pos();

async_reset_signal_is( rst, false);// active low asynchronous reset

```

### SC\_CTHREAD example:

```

SC_CTHREAD(thread_process, clk.pos());

async_reset_signal_is( rst, false);// active low asynchronous reset

```

### 4.2.2 Thread process body

In a SystemC <u>application</u>, it is a common coding idiom to include an infinite loop containing a call to the *wait()* function within a thread process in order to prevent the process from terminating prematurely, at the same time allowing co-operative pre-emption during simulation by suspending the process. The thread process body of a <u>design shall</u> also follow this structure. Among the available constructs to suspend a process, a <u>design shall</u> only use a call to *wait()*, where the wait condition is the clock edge to which the thread process is sensitive, as specified in the module constructor. That is, the only **Supported** waits are the following.

- *wait()*

- *wait(int)*: where the integer argument is statically determinable.

Other forms of suspending a thread process are *Not Supported*.

The behavior of a thread process consists of reset behavior, which executes on reset, and operational behavior, which executes after reset.

The body of the thread process in a *design shall* follow the form:

[<optional reset behavior>] [<optional operational behavior>] <infinite loop> subject to the restrictions below

The reset and operational behavior <u>shall</u> be separated by a call to the *wait()* function. Any behavior encountered in the thread process prior to encountering the first call to the *wait()* function <u>shall</u> be considered by the <u>synthesis tool</u> as reset behavior. Any behavior encountered in the thread process after encountering the first call to the *wait()* function <u>shall</u> be considered by the <u>synthesis tool</u> as operational behavior.

The first call to the *wait()* function <u>may</u> occur before the infinite loop, or it <u>may</u> occur within the infinite loop. In the case where the first call to the *wait()* function occurs within the infinite loop, the behavior within the loop body prior to the first call to the *wait()* function <u>shall</u> be considered by the <u>synthesis tool</u> to be both reset behavior and operational behavior.

Multiple calls to the *wait()* function <u>may</u> occur within the body of the thread process, both before the infinite loop, and within the body of the infinite loop. The behavior encountered before the first call to the *wait()* function <u>shall</u> be the reset behavior; any behavior encountered after the first call to the *wait()* function <u>shall</u> be the operational behavior.

Within the body of the thread process, the first call to the *wait()* function *shall* be statically determinable. The first call to the *wait()* function *may* be within conditional constructs only when the condition is statically determinable (e.g., in the case where the condition is based on a template parameter). Subsequent calls to the *wait()* function (in the operational behavior) *may* occur within conditional constructs.

Reset values *shall* be statically determinable constants.

The following forms of infinite loop are *Supported*, others are *Not Supported*.

while(1) { }

while(true) { }

do { } while(1);

do { } while(1);

for(;;) { }

#### NOTE

```

Example of SC_THREAD/SC_CTHREAD body:

void dut::thread process() {

// Reset behavior goes here

wait(); // This wait separates reset behavior from

// operational behavior.

// You can operational behavior here

while(1) { // Repeated operational behavior.

// The infinite loop prevents the operational behavior

// from terminating.

wait(); // This wait allows suspension of the process.

}

}

void dut::thread_process() {

// Reset behavior goes here

// You cannot have operational behavior here, because there

// is no wait() to separate them from reset behavior.

while(1) {

// The infinite loop prevents the process from terminating

// Behavior here is both reset behavior and operational

// behavior.

wait(); // This wait separates reset behavior from

// operational behavior and also allows suspension

// of the process.

//operational behavior

}

```

#### NOTE

Reset behavior is behavior that is executed when reset is asserted. As Section 3.1.3.5 indicates, writing to data members, signals, or ports of a module from inside the *SC\_MODULE* constructor is not reset behavior. Default constructors of data members of the *SC\_MODULE* that initialize the data members (e.g., the default constructor for *sc\_int* initializes the value to 0), are not part of the reset behavior. If the behavior of the *design* depends on those non-reset initial values, then synthesis results might differ from simulation

```

results.

Example:

class X {

public:

X() {

m_1 = 0;

}

private:

int m_1;

};

class XChild : public X {

};

SC_MODULE(Module) {

sc_signal< X > xSig;

sc_signal< XChild > xChildSig;

sc_in_clk clk;

sc_in<bool> rst;

SC_CTOR(Module)

: xSig("xSig"), // Warning! Synthesis will Not invoke default ctor for X.

xChildSig("xChildSig") //Warning! Synthesis will Not invoke

//default constructor for XChild.

{

SC_CTHREAD(proc, clk.pos());

reset_signal_is(rst, true);

}

void proc() {

// Reset clause

X x_tmp;

// OK. Invoke default constructor for X.

xSig = x_tmp;

// OK. Initialize xSig with x_tmp.

xChildSig = XChild(); // OK. Initialize xChildSig by the

/ / default constructor.

wait();

// Main loop

while (true) {

. . .

}

}

};

```

## **5** Predefined channels, interface proper and ports

### 5.1 **Predefined Channels**

### 5.1.1 sc\_signal

*sc\_signal* has *Restricted Support*. Use of a *sc\_signal* with the *WRITER\_POLICY* defaulted or explicitly set to *SC\_ONE\_WRITER* is *Supported*. Use of a *sc\_signal* with the *SC\_MANY\_WRITERS* policy is *Not Supported*.

Furthermore, only the following member functions are *Supported*.

| <i>void write( const T&amp; )</i>                                                |

|----------------------------------------------------------------------------------|

| const T& read()                                                                  |

| <pre>sc_signal(), sc_signal(string), and sc_signal( signal )</pre>               |

| operator = (const T &)                                                           |

| <pre>operator= ( const sc_signal<t,writer_policy>&amp; )</t,writer_policy></pre> |

Arrays of *sc\_signal* are *Supported*.

### 5.1.2 Resolved Channels

Resolved types are *Not Supported*. This includes *sc\_signal\_resolved*, *sc\_in\_resolved*, *sc\_inout\_resolved*, *sc\_out\_resolved*, *sc\_signal\_rv*, *sc\_inout\_rv*, *sc\_inout\_rv*, and *sc\_out\_rv*.

### 5.1.3 Other Channels

The following list of pre-defined SystemC channels are also *Not Supported*: *sc\_buffer*, *sc\_clock*, *sc\_mutex*, *sc\_semaphore*, *sc\_fifo*, and *sc\_event\_queue*.

#### NOTE

While *sc\_clock* channel is not supported, clock ports are supported as specified in Section 5.2.1.

### 5.2 **Ports**

The pre-defined specialized port classes are *Supported* so blocks in a SystemC hierarchy can communicate through convenient access to member functions of the pre-defined SystemC primitive channels.

#### 5.2.1 sc\_in, sc\_out, and sc\_inout

sc\_in<T> and sc\_out<T> for T being any synthesizable type are Supported. sc\_in<bool>, and sc\_in\_clk are all Supported. sc\_in<sc\_dt::sc\_logic> is Not Supported. sc\_inout<T> is Not Supported.

Furthermore, for *sc\_in*<*T*>, only the following member functions are *Supported*.

| <pre>sc_in() and sc_in(const char*)</pre>                 |  |

|-----------------------------------------------------------|--|

| const T& read() const                                     |  |

| operator const T& () const                                |  |

| <pre>void bind( const sc_signal_in_if<t>&amp; )</t></pre> |  |

| <pre>void operator() ( const sc_signal_in_if<t> &amp; )</t></pre>                 |

|-----------------------------------------------------------------------------------|

| void bind( sc_port< sc_signal_in_if <t>, 1&gt; &amp; )</t>                        |

| <pre>void operator() ( sc_port&lt; sc_signal_in_if<t>, 1&gt; &amp; )</t></pre>    |

| void bind( sc_port< sc_signal_inout_if <t>, 1&gt; &amp; )</t>                     |

| <pre>void operator() ( sc_port&lt; sc_signal_inout_if<t>, 1&gt; &amp; )</t></pre> |

For *sc\_in<bool>*, in addition to the above, the following further member functions are *Supported*.

| <pre>sc_event_finder&amp; pos() const</pre> |  |

|---------------------------------------------|--|

| <pre>sc_event_finder&amp; neg() const</pre> |  |

Furthermore, for *sc\_out*<*T*>, only the following member functions are *Supported*.

| <pre>sc_out() and sc_out(const char*)</pre>                          |

|----------------------------------------------------------------------|

| const T& read() const                                                |

| operator const T& () const                                           |

| void write( const T& )                                               |

| operator = (const T&)                                                |

| operator= ( const sc_signal_in_if <t>&amp; )</t>                     |

| operator= ( const sc_port< sc_signal_in_if <t>, 1&gt; &amp; )</t>    |

| operator= ( const sc_port< sc_signal_inout_if <t>, 1&gt; &amp; )</t> |

| $operator = (const sc_out < T > \&)$                                 |

| <pre>void bind( const sc_signal_inout_if<t>&amp; )</t></pre>         |

| <pre>void operator() ( const sc_signal_inout_if<t> &amp; )</t></pre> |

For *sc\_out<bool>*, in addition to the above, the following further member functions are *Supported*.

| sc_event_finder& pos() const |  |

|------------------------------|--|

| sc_event_finder& neg() const |  |

Arrays of ports are *Supported*.

Inheriting from the specialized port types is *Not Supported*.

### 5.3 sc\_event

sc\_event in a *design* is *Not Supported*.

## 6 Types

SystemC types are comprised of both the native C++ types and the additional SystemC types.

There are two kinds of native C++ types: fundamental types and compound types. Types describe objects, references, or functions.

### NOTE

Alignment requirements mentioned in ISOC++ 3.9 are not relevant for synthesis.

Synthesis may choose alternative data representations for internal objects (not part of the interface of the *design*) provided the I/O behavior of the *design* is unchanged. For example, the bit-width of an integer variable could be reduced based on the range of the variable or its representation could be changed from two's complement to sign-magnitude.

### 6.1 **Fundamental Types**

Fundamental types are comprised of integer types, floating-point types, and void.

### 6.1.1 Integer Types

The following integer types, as specified in ISOC++ and ISOC++11 3.9.1, are *Supported*:

- bool

- unsigned char, signed char, char

- unsigned short, signed short

- unsigned int, signed int

- unsigned long, signed long

- *unsigned long long, signed long long* (ISOC++ 11)

The integer type *wchar\_t* is *Not Supported*.

### NOTE

ISOC++ 3.9.1 specifies that it is implementation defined whether a *char* object can hold negative values; GNU G++ can support either mode through use of the "-

*fsigned\_char/unsigned\_char*" switch. The <u>synthesis tool</u> vendor is likely to choose the mode that best meets the architecture for which their simulation model was built in order to achieve consistent results between simulation and synthesis models.

ISOC++ 3.9.1 also specifies that plain *char*, *signed char*, and *unsigned char* are three distinct types. Even if a particular implementation allows a *char* to hold negative values, it is not the same type as a *signed char*.

### 6.1.1.1 Literals

Integer and Boolean literals, as specified in ISOC++ 2.13.1 and 2.13.5, are *Supported*.

Character literals as described in ISOC++ 2.13.2 have *Restricted Support*. The *L* prefix denoting wide character support is *Not Supported*.

For synthesis, if the numerical value of the *char* literal has an effect on functionality (the exception being comparing *chars* for equality), characters <u>shall</u> be assumed to be encoded in the ASCII character set. This is a <u>synthesis refinement</u> over ISOC++ 2.13.2 and 2.13.4, which allows alternative execution character sets (ISOC++ Section 2.2, Paragraph 3).

### 6.1.1.2 **Representation and Bit Sizes**

Two's complement integer representations are *Supported*. One's complement and sign magnitude integer representations are *Not Supported*.

A <u>synthesis tool shall</u> have mechanisms to support the I/O observable behavior implied by bitwidths and representation for the computer platforms as indicated in the last column of the table below. It <u>shall</u> warn in case the choice of bit-width or the representation is not consistent with the definition for the computer platform.

| Integer               | Relative                         | Current Compilers |       |  |

|-----------------------|----------------------------------|-------------------|-------|--|

| Туре                  | Requirement                      | ement Signed      |       |  |

|                       |                                  | Representation    |       |  |

| (un)signed char, char |                                  | two's complement  | 8     |  |

| (un)signed short      | $bits(short) \ge bits(char)$     | two's complement  | 16    |  |

| (un)signed int        | $bits(int) \ge bits(short)$      | two's complement  | 32    |  |

| (un)signed long       | $bits(long) \ge bits(int)$       | two's complement  | 32/64 |  |

| (un)signed long long  | $bits(long long) \ge bits(long)$ | two's complement  | 64    |  |

#### Table 1: Bit Sizes for Integer Types

#### NOTE

1: The representation and the bit-width of an integer type determines its numerical range and its overflow behavior.

2: The ISOC++ and ISOC++11 standards set minimum requirements for the bit widths of integer types, but leave bit widths and the representation implementation-dependent.

3: ISOC++ 3.9.1 specifies unsigned integers <u>shall</u> obey the laws of arithmetic module  $2^n$ , where *n* is the number of bits. Signed integers are of a pure binary numeration system and the representations allowed are two's complement, one's complement, and sign magnitude.

4: Table 1 provides an overview of the ISOC++ 3.9.1 requirements and bits sizes for integer types used on most compilers for popular computer platforms. It constrains the relative sizes of the different integer types, and also requires the signed and unsigned (and plain in the case of characters) versions of integer types to have the same storage. The last column in the table shows the bit widths for current platforms. As the table indicates, there is only a difference for the (un)signed long types in current platforms.

5: ISOC++11 provides typedefs for "exact-width" integer types. These are *intN\_t* and *uintN\_t*, where N can be 8, 16, 32, or 64. The typedefs are defined in the *std* namespace in the include *<cstdint>* header. For example, int64\_t is defined as *long* on platforms where *long* is 64-bits wide and as *long long* on platforms where *long* is 32-bits wide.

#### 6.1.2 Type Conversions

Type conversions are *Supported* as specified in the sections below.

### NOTE

ISOC++ defines two kinds of conversions between integer types that are applied in the evaluation of expressions: integer promotions and usual arithmetic conversions.

An example of an integer promotion is when a *short* is promoted to an *int* in the unary minus expression "-a" (variable "a" is of type *short*).

The usual arithmetic conversions are defined by the C++ language to yield a common type for many binary operators that expect operands of arithmetic or enumeration type.

An example of a usual arithmetic conversion is when an operand of type *short* is converted to *long long* in the expression "a+b" where "a" is of type *short* and "b" is of type *long long*. In that case, "a" is first promoted to type *int* (integer promotion that is performed as part of the usual arithmetic conversion) and then converted to *long long*.

### 6.1.2.1 Integer Promotions

Integer (Integral) Promotions (as defined in ISOC++ 4.5) are *Supported*.

### 6.1.2.2 Usual Arithmetic Conversions

Usual Arithmetic Conversions (as defined in ISOC++ Section 5 and ISOC++11 4.5 corresponding to the addition of the *long long* types) are *Supported*.

### 6.1.3 Operators

The following operators are *Supported* for the integer types:

- 1. Unary operators  $(+, -, \sim, and!)$ .

- 2. Arithmetic binary operators (+, -, \*, /, and %) and the corresponding assign operators (+=, -=, \*=, /=, and %=). The result of division is truncated towards zero (0) as specified in ISOC++11 5.6.

- 3. Relational and Equality operators (>, >=, <, <=, ==, and !=).

- 4. Bitwise binary operators (&, |, and ^) and the corresponding assign operators (&=, |=, and ^=).

- 5. The Conditional Operator (?:).

### NOTE

The ~ operator on a *bool* argument x first promotes it to an *int* and then computes the one's complement (value is -x-1) of the promoted value (ISOC++ 5.3.1).

bool x = true; int y =  $\sim$ x; // y is -2 bool z =  $\sim$ x; // z is true

If the intended behavior is to get the logical complement, the logical negation operator ! (ISOC++ 5.3.1) should be used.

The following operators have *Restricted Support*.

- 1. Shift and shift assign operators (<<, >>, <<=, and >>=). Considering *E1* and *E2* as the two operands (as in "*E1 shift\_op E2*"), the support is as follows.

- a. ISOC++ 5.8 specifies that valid ranges for *E2* is 0 to *length(promoted\_type(E1))*-1 and that otherwise the behavior is undefined (Section 1.5.2). Shifts are *Supported* for valid ranges and *Not Supported* otherwise.

- b. For right shifts, if *E1* has a signed type, the sign bit <u>shall</u> be shifted in. This is a <u>synthesis refinement</u> on ISOC++ and ISOC++11, since these standards leave the behavior implementation-defined when *E1* is negative.

- c. For left shifts, the behavior specified in ISOC++ with the natural implications due to the addition of the *long long* types are presumed in this standard.

- 2. The prefix and postfix increment and decrement operators (++x, --x, x++, and x--) have *Restricted Support*. The restriction is that the prefix and postfix increment operators on a *bool* operand are *Not Supported* as they are deprecated by ISOC++.

### 6.1.4 Floating Point Types

Floating literals (as specified in ISOC++ 2.13.3) are *Supported* for initializing synthesizable datatypes. If the floating literal is used to initialize an integer type (a floating-integral conversion is involved as specified in ISOC++ 4.9) and the truncated value is not representable in the integer type, then the behavior is undefined (see Section 1.5.2).

Otherwise, floating-point types (specified in ISOC++ 3.9.1 as *float*, *double*, and *long double*) are *Not Supported*.

#### NOTE

One of the challenges for providing general synthesis support for floating-point datatypes is the fact that the bit accurate behavior of floating point arithmetic is dependent on implementations and compiler options used [4].

### 6.1.5 The void type

The *void* type (ISOC++ 3.9.1) is *Supported*.

### 6.2 **Compound Types**

Compound types in C++, as described in ISOC++ 3.9.2, have *Restricted Support* determined by the support restrictions of the constituent types.

### 6.3 SystemC Datatypes

SystemC provides a number of datatypes that are useful for hardware design. These datatypes are implemented as C++ classes.

The following SystemC types have *Restricted Supported* as described in the sections below:

- Limited Precision Integer Types: *sc\_int* and *sc\_uint* (Section 6.3.1)

- Finite Precision Integer Types: *sc\_bigint* and *sc\_biguint* (Section 6.3.2)

- Finite Precision Fixed-point Types: *sc\_fixed* and *sc\_ufixed* (Section 6.3.3)

- Finite Word-Length Bit Vector Type: *sc\_bv* (Section 6.3.4.1)

- Finite Word-Length Logic Vector Types (4-valued): *sc\_lv* (Section 6.3.4.2)

- Single Bit Logic (4-valued): *sc\_logic* (Section 6.3.4.2)

The explicit use of SystemC datatypes that are not in the list above is *Not Supported*. The implicit use of other related types that arise as return types from operators on the types listed above has *Restricted Support*. The restriction is that the bitwidth of a return type needs to be statically determinable.

#### NOTE

1: All datatypes supported for synthesis have vector length/precision that is specified by template parameters. Thus, their vector length/precision is statically determinable during compilation.

2: Underlying classes, such as *sc\_signed* and *sc\_unsigned*, can appear as the result of expression on supported types, but are not directly synthesizable. Their length/precision is dynamic. Some base and helper classes are specifically denoted in SystemC LRM 3.2.4 as classes that should not be used explicitly. The SystemC LRM annotates those classes with a superscript dagger ( $^{\dagger}$ ).

#### 6.3.1 Limited Precision Integer Types

SystemC LRM 7.5.2 and 7.5.3 state that the finite precision *sc\_int/sc\_uint <u>shall</u>* be held in an implementation-dependent native C++ integer which <u>*shall*</u> have a minimum representation size of 64 bits. For synthesis, representation sizes greater than 64-bits are *Not Supported*.

In summary, the following types have *Restricted Supported*.

- $sc_i < W >:$  limited precision signed integer ( $W \le 64$ ).

- $sc\_uint < W >$ : limited precision unsigned integer ( $W \le 64$ ).

Support restrictions on operators and functions are covered in Section 6.3.5. Many operators are available through implicit conversions to *int\_type* and *uint\_type* and their support is determined by the support of those native C++ types.

#### 6.3.2 Finite Precision Integer Types

The following Finite Precision Integer types have *Restricted Support*.

- *sc\_bigint*<*W*>: finite precision signed integer.

- *sc\_biguint*<*W*>: finite precision unsigned integer.

The support restrictions of common operators and functions are covered in Section 6.3.5.

#### 6.3.3 Finite Precision Fixed-point Types

The fixed-point types *sc\_fixed* and *sc\_ufixed* have *Restricted Support* as listed below.

- 1. Overflow modes have *Restricted Support* as specified in Table 2 below as a function of the two template parameters that determine the overflow mode: *o\_mode* and *n\_bits*.

- 2. All Quantization modes are *Supported* as specified in Table 3 below as a function of the template parameter that determines the quantization mode: *q\_mode*.

- 3. Common operators/functions: see Section 6.3.5.

- 4. Specific member functions:

- a. Query of parameters: *wl*, *iwl*, *q\_mode*, *o\_mode*, and *n\_bits* are *Supported*.

- b. Query of value: *is\_neg*, *is\_zero*, and *value* are *Not Supported*.

- c. Other member functions such as *overflow\_flag*, *quantization\_flag*, *type\_params*, and *cast\_switch* are *Not Supported*.

- 5. Simulation specific functionality such as *sc\_fxtype\_param*, *sc\_fxcast\_switch*, and *SC\_OFF* are *Not Supported*.

Table 2: Overflow Modes

| Overflow Mode                        | Parameters  |          | Support       |

|--------------------------------------|-------------|----------|---------------|

|                                      | o_mode      | n_bits   |               |

| Wrap-around Basic ( <i>default</i> ) | SC_WRAP     | 0        | Supported     |

| Saturation                           | SC_SAT      | -        | Supported     |

| Symmetrical Saturation               | SC_SAT_SYM  | -        | Supported     |

| Saturation to Zero                   | SC_SAT_ZERO | -        | Supported     |

| Wrap-around Advanced                 | SC_WRAP     | >0       | Not Supported |

| Sign Magnitude Wrap-Around           | SC_WRAP_SM  | $\geq 0$ | Not Supported |

#### Table 3: Quantization Modes

| Quantization Mode             | Parameter (q_mode) | Support   |

|-------------------------------|--------------------|-----------|

| Truncation ( <i>default</i> ) | SC_TRN             | Supported |

| Rounding to plus Infinity     | SC_RND             | Supported |

| Truncation to zero            | SC_TRN_ZERO        | Supported |

| Rounding to zero              | SC_RND_ZERO        | Supported |

| Rounding to minus infinity    | SC_RND_MIN_INF     | Supported |

| Rounding to infinity          | SC_RND_INF         | Supported |

| Convergent rounding           | SC_RND_CONV        | Supported |

#### 6.3.4 Logic and Vector Types

#### 6.3.4.1 **Finite Word-Length Bit Vectors (sc\_bv)**

The finite word-length bit vector *sc\_bv* has *Restricted Support*. The restrictions on common operators/functions are outlined in Section 6.3.5.

#### 6.3.4.2 Single-Bit Logic (sc\_logic) and Finite Word-Length Logic Vectors (sc\_lv)

The single-bit logic  $sc_logic$  and the finite world-length logic vector  $sc_lv$  have **Restricted Support**. The restriction on common operators/functions are outlined in Section 6.3.5. In addition, the following restrictions apply.

- The unknown logic constant (*sc\_logic* ("X"), *SC\_LOGIC\_X*) is *Not Supported*.

- The high-impedance logic constant (*sc\_logic* ("Z"), *SC\_LOGIC\_Z*) is *Not Supported*.

#### 6.3.5 Common Operators and Functions

#### 6.3.5.1 **Bit Select Operator**

The bit select operators as specified by SystemC LRM 7.2.5 have *Restricted Support*. The restriction is that the index is within the bounds of the object being accessed.

#### NOTE

An out-of-bound access will be treated as an error by synthesis as defined in Section 1.6.3.

The bit select *operator[i]* allows the selection of a bit of a variable either as an *rvalue* or an *lvalue*.

As defined by SystemC LRM 7.5.4.6, *sc\_int/sc\_uint* temporary values cannot have bit-select applied.

As defined by SystemC LRM 7.7 and 7.5.7, the bit select on concatenations or subreferences also cannot be performed.

Example:

```

sc_int< 8 > x ;

sc_bigint< 8 > y ;

x[3] = y[2] // Legal

(x+x)[3] = 0 ; // Illegal, as x+x is promoted to a native C++ type

(y+y)[3] = 0 ; // Legal as y+y is still a sc_bigint

(y,y)[3] = 0 ; // Illegal as concatenation doesn't support bitref

```

#### 6.3.5.2 **Part Select Operator**

The part select operators (*operator*(l,r) and *range*(l,r)), as specified by SystemC LRM 7.2.6, have *Restricted Support*. The first restriction is both the left and the right index positions lie within the bounds of the object. The second restriction is the range of the part select has a statically determinable length. The third restriction is the left hand index is greater or equal to the right hand index.

Out-of-bound access <u>shall</u> be treated as an error (Section 1.6.3), as specified in the SystemC LRM.

NOTE

The third restriction implies bit-reversal using part selects is not supported. Given the second restriction, the third restriction becomes trivial to check.

The bit-reversal behavior is specified for fixed-point types, as specified in SystemC LRM 7.10.5. It is also implied for vector types in the specification of *reversed* in SystemC LRM 7.9.8.7. Part select is not allowed to reverse bit-order for limited-precision integers, as stated in NOTE1 in SystemC LRM 7.2.6. The SystemC LRM does not explicitly mention whether part selects are allowed to reverse bit-order for finite-precision integers.

Example of statically determinable range length: x(i+5,i+3) = y(k+4,k+2); // range length = 3

#### NOTE

As defined by SystemC LRM 7.5.4.6, *sc\_int/sc\_uint* temporary values cannot have part-select applied.

Part select is not available for concatenations and subrefs of integer types. Part select is available for concatenations and subrefs of vector types ( $sc_bv$  and  $sc_lv$ ).

Example:

```

sc_int< 8 > x ;

sc_bigint< 8 > y ;

```

```

x(5,3) = y(4,2); // Legal

(x+x)(5,3) = 0; // Illegal: x+x is promoted to native C++ type

(y+y)(5,3) = 0; // Legal as y+y is still a sc_bigint

(y,y)(5,3) = 0; // Illegal: concatenation of bitref not allowed

```

The result of a part select cannot be directly assigned to a fixed point variable, but it can be assigned to a range.

#### 6.3.5.3 Function concat(C1,C2) and operator,(C1,C2)

The concatenation function and operator are *Supported*.

NOTE

The SystemC datatype package defines concatenation functionality via a template specialized function concat(C1, C2) and operator, (C1, C2).

The concatenation operation (*op1,op2*) may be used as an *rvalue* or an *lvalue*.

Example:

(x, y) = (z, w);

Because of the difference in return types for operators for *sc\_bigint/sc\_biguint* and *sc\_int/sc\_uint*, using expressions (unless they are cast) may give different results for arbitrary precision integers than for finite precision integers. Using uncast expressions other than concatenation, bit select, and part select as arguments of the concatenate operation is not recommended. For example, using the Accellera Open Source simulator:

```

sc_int<4> t = 1; sc_bigint<4> tb = 1;

sc_int<4> x = 2; sc_bigint<4> xb = 2;

cout << (t, t*x) << endl; // result = 3

cout << (t, tb*xb) << endl; // result = 258

cout << (t, x >> 1) << endl; // result = 3

cout << (t, xb >> 1) << endl; // result = 17</pre>

```

#### 6.3.5.4 **Reduction Operators**

The reduction operators specified in SystemC LRM 7.2.8 are Supported.

NOTE

The reduce operators are: *and\_reduce*, *or\_reduce*, *xor\_reduce*, *nand\_reduce*, *nor\_reduce*, and *xnor\_reduce*.

The reduction operators are not available for the fixed-point datatypes.

#### 6.3.5.5 Arithmetic Operators

The arithmetic operators for limited and finite precision integers, as defined in the SystemC LRM, are *Supported*.

The arithmetic operators for the finite precision fixed-point types, as defined in the SystemC LRM, have *Restricted Support*. The implementation-dependent behavior described in SystemC LRM 7.10.6 (variable-precision fixed-point value limits) is *Not Supported*. A consequence is that the division operator is *Not Supported*.

#### NOTE